Difference between revisions of "Serial ULA"

m (→SERPROC extension: fix link) |

(→Control register: *FX242 warning) |

||

| Line 24: | Line 24: | ||

''The preferred methods to update the control register are via [[OSBYTE]] calls [[OSBYTE &07|7]], [[OSBYTE &08|8]], [[OSBYTE &89|137 (&89)]] and [[OSBYTE &CD|205 (&CD)]] or the <code>*MOTOR</code> command.'' Between them | ''The preferred methods to update the control register are via [[OSBYTE]] calls [[OSBYTE &07|7]], [[OSBYTE &08|8]], [[OSBYTE &89|137 (&89)]] and [[OSBYTE &CD|205 (&CD)]] or the <code>*MOTOR</code> command.'' Between them | ||

these calls provide complete control over the ULA whilst the [[CFS|Cassette | these calls provide complete control over the ULA whilst the [[CFS|Cassette | ||

| − | Filing System]] is inactive. <code>[[OSBYTE &97|*FX | + | Filing System]] is inactive. Neither <code>[[OSBYTE &97|*FX |

| − | 151]],16,<var>n</var></code> should | + | 151]],16,<var>n</var></code> nor <code>[[OSBYTE &F2|*FX |

| − | + | 242]],<var>n</var></code> should be used as these put the physical control | |

| − | + | register and the related MOS variables into an inconsistent state. | |

The register is summarised as follows: | The register is summarised as follows: | ||

Latest revision as of 22:44, 30 August 2021

The serial ULA is a custom Integrated Circuit (IC) developed by Acorn Computer for use in its BBC Microcomputer series. It shares the 6850 ACIA between the cassette port and serial port, provides a clock for the ACIA, and modulation, demodulation and motor control for the cassette port.

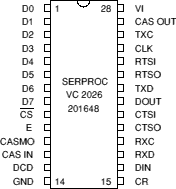

The original IC was fabricated by Ferranti as an Uncommitted Logic Array (ULA), permanently mask-programmed to Acorn's specification; part number ULA 2C199E. Later, Acorn second-sourced the chip from VLSI Technology, Inc.; this was a different design, more correctly known as the SERPROC (Serial Processor); part number VC 2026, Acorn part number 201,648. With one exception this was functionally and physically compatible with the serial ULA.

Contents

Interface

Control register

The serial ULA control register appears in SHEILA at address &FE10. It is a write-only register but the MOS maintains a copy in RAM at address &282, and a related flag at address &25D.

The preferred methods to update the control register are via OSBYTE calls 7, 8, 137 (&89) and 205 (&CD) or the *MOTOR command. Between them

these calls provide complete control over the ULA whilst the Cassette

Filing System is inactive. Neither *FX

151,16,n nor *FX

242,n should be used as these put the physical control

register and the related MOS variables into an inconsistent state.

The register is summarised as follows:

| b7 | b6 | b5, | b4, | b3 | b2, | b1, | b0 |

|---|---|---|---|---|---|---|---|

| Cassette motor on | Serial port enabled | Receive clock rate | Transmit clock rate | ||||

The clock rate fields are defined as follows:

| b5 | b4 | b3 | Receive clock rate | Receive baud rate (÷ 64) | *FX 7,n |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1228.8 kHz | 19200 baud | 8 |

| 1 | 0 | 0 | 614.4 kHz | 9600 baud | 7 |

| 0 | 1 | 0 | 307.2 kHz | 4800 baud | 6 |

| 1 | 1 | 0 | 153.6 kHz | 2400 baud | 5 |

| 0 | 0 | 1 | 76.8 kHz | 1200 baud | 4 |

| 1 | 0 | 1 | 19.2 kHz | 300 baud | 3 |

| 0 | 1 | 1 | 9.6 kHz | 150 baud | 2 |

| 1 | 1 | 1 | 4.8 kHz | 75 baud | 1 |

| b2 | b1 | b0 | Transmit clock rate | Transmit baud rate (÷ 64) | *FX 8,n |

The 19200 baud rate setting is not guaranteed.[1] These are nominal values — actual rates are 0.16 percent higher as they are derived from a (16/13) MHz clock.

In serial mode the MOS fixes the clock divider of the ACIA at '÷ 64', giving the baud rates listed above. The default value of the control register is &64 (motor off, serial port enabled, 9600 baud receive and transmit.)

In cassette mode the MOS writes the hard-coded value &85 to the control register (motor on, cassette enabled, 19200 baud receive, 300 baud transmit) and sets the ACIA clock divider to '÷ 16' for the 1200 baud Acorn format, or '÷ 64' for the 300 baud CUTS format. '÷ 1' selects the often-mentioned 'third baud rate' of 19200 baud, which is quite unusable. (The ULA only emits whole 2400 Hz cycles or whole 1200 Hz cycles, so much of the data is lost.)

The ULA itself ignores bits 5 to 3 and generates a receive clock of 19.2 kHz when bit 6 is clear. (The SERPROC also disregards bits 5 and 4 but reassigns bit 3 for another purpose, see below.) When saving, bits 2 to 0 as well as the ACIA clock divider govern the baud rate, as in serial mode, but again the MOS only adjusts the divider.

SERPROC extension

While the cassette port is active, bit 3 of the VLSI chip's register controls modulation and demodulation tone levels.

| b6 | b3 | Port enabled | Logical 0 | Logical 1 | Receive clock rate | Compatibility |

|---|---|---|---|---|---|---|

| 1 | x | Serial port | +5V | −5V | set by b5–b3 | RS 423 |

| 0 | 1 | Cassette port | 2400 Hz | 1200 Hz | 19.2 kHz | Ohio Scientific computers, UoSAT-1, ITU-T V.1 |

| 0 | 0 | Cassette port | 1200 Hz | 2400 Hz | 19.2 kHz | Acorn computers, UoSAT-2, BASICODE |

The Chip Shop's BASICODE 2 (1984) falls foul of the extension. It sets bit 3 = 1 and assumes logical 0 will remain at 1200 Hz, making it compatible only with the Ferranti ULA. ASK's Facemaker and Icon's Caveman Capers fail to load for the same reason. All three can be read through the SERPROC if the custom-loaded portions are played with the frequencies swapped. (Pace's Fortress does not yield so easily; the level change when the SERPROC is reprogrammed provokes an unexpected framing error from the ACIA, which hangs the Fortress load routine.) Alternatively one small modification to Fortress or the BASICODE loader[2] will make both Ferranti and VLSI parts accept the streams as published.

Pinout[3]

Notes

An issue was identified with the Ferranti ULA whereby it would sometimes need to be 'thumped' in software before it would recognise cassette files. The 'thump' involved turning the cassette motor off, then quickly on after the motor has been turned on with an official call. The workaround was included in the MOS.[4]

References

- ↑ Acorn Computer, The BBC Micro User Guide.

- ↑ See VLSI SERPROC compatible versions of Basicode 2, Caveman Capers, Facemaker and Fortress.

- ↑ Based on the circuit diagram for BBC Microcomputer

- ↑ The Micro User, August 1983, p.85.

-- beardo 17:07, 16 December 2008 (UTC)